前言

Arm架构是一个用于计算机处理器的RISC指令集架构系列,针对各种环境进行配置。Arm开发这些架构并将其授权给其他公司,这些公司设计自己的产品来实现一种或多种这些架构,包括片上系统(SoC) 和模块上系统(SOM) 设计,其中包含不同的组件,例如内存、接口和无线电。

Arm公司还设计核心实现这些指令集架构并将这些设计授权给许多公司,这些公司将这些核心设计融入到自己的产品中。 由于与竞争对手相比,ARM 处理器成本低、功耗低、发热量低,因此非常适合轻型、便携式、电池供电的设备,包括智能手机、笔记本电脑和平板电脑以及其他嵌入式系统。

ARM Company Wiki:https://en.wikipedia.org/wiki/Arm_(company)

ARM Architecture Wiki:https://en.wikipedia.org/wiki/ARM_architecture_family

ARM Procssor Wiki:https://en.wikipedia.org/wiki/List_of_ARM_processors

1. Cortex-X CPU

Cortex-X1

ARM Cortex-X1是执行ARMv8.2-A 64 位指令集的中央处理单元,由ARM Holdings奥斯汀设计中心设计,是 ARM Cortex-X Custom (CXC) 计划的一部分。

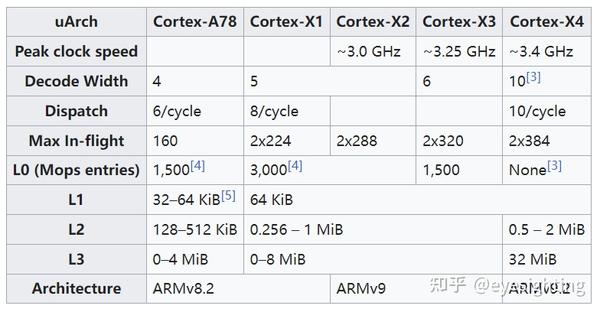

Cortex-X1 设计基于ARM Cortex-A78,但经过重新设计,纯粹是为了性能,而不是性能、功耗和面积 (PPA) 的平衡。Cortex-X1 是一种 5 宽解码乱序 超标量设计,具有 3K 宏 OP (MOP) 缓存。它每个周期可以获取 5 条指令和 8 个 MOP,并且每个周期可以重命名和分派 8 个 MOP 和 16 µOP。无序窗口大小已增加至 224 个条目。后端有 15 个执行端口,管道深度为 13 级,执行延迟由 10 级组成。它还具有 4x128b SIMD 单元。

ARM 声称 Cortex-X1 的整数运算速度比ARM Cortex-A77快 30%,机器学习性能快 100% 。Cortex-X1支持ARM的DynamIQ技术,与ARM Cortex-A78中核和ARM Cortex-A55小核结合使用时,预计将用作高性能内核。

Cortex-X1:https://en.wikipedia.org/wiki/ARM_Cortex-X1

Cortex-X1:https://en.wikipedia.org/wiki/ARM_Cortex-X1

Cortex-X1:Arm Cortex-X1: The First From The Cortex-X Custom Program

Cortex-X2ARM

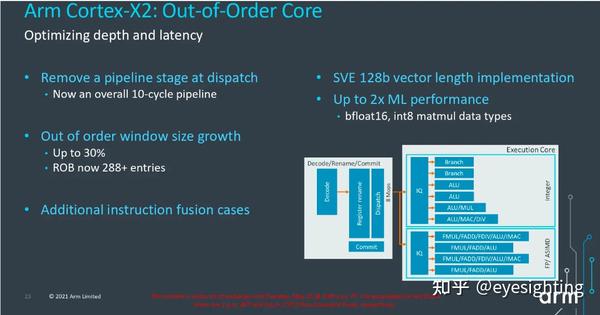

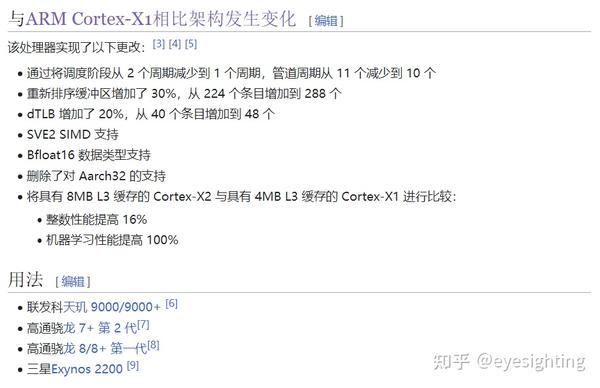

Cortex-X2是一个中央处理单元,实现ARMv9-A 64 位指令集,由ARM Holdings奥斯汀设计中心设计,作为 ARM Cortex-X 定制 (CXC) 计划的一部分。

Cortex-X2:https://en.wikipedia.org/wiki/ARM_Cortex-X2

Cortex-X2:Arm Launches Its New Flagship Performance Armv9 Core: Cortex-X2

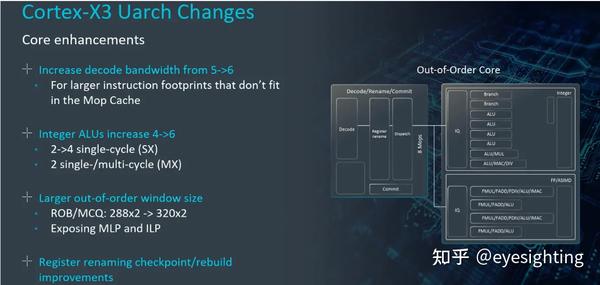

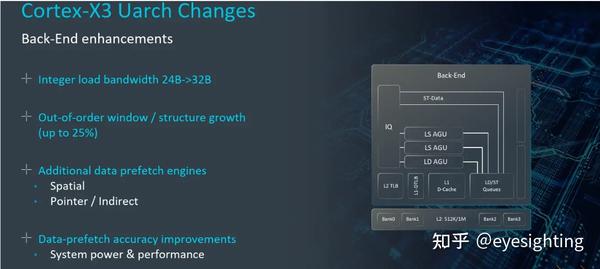

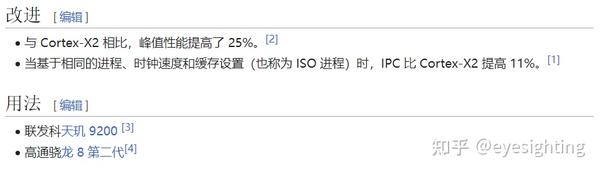

Cortex-X3

ARM Cortex-X3是Arm第三代 X 系列高性能 CPU 内核。

Cortex-X3:https://en.wikipedia.org/wiki/ARM_Cortex-X3

Cortex-X3:Arm Unveils Next-Gen Flagship Core: Cortex-X3

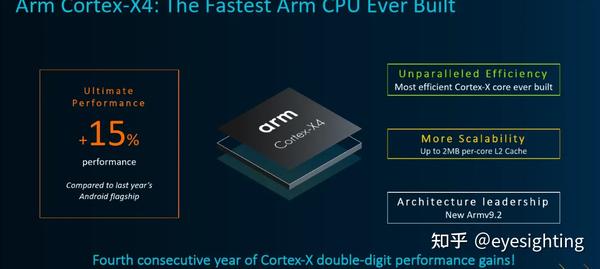

Cortex-X4

ARM Cortex-X4是Arm的CPU 核心模型。它在 TCS23 中推出,作为ARM Cortex-X3的后继产品,X 系列 CPU 内核通常注重高性能,并且可以与该系列中的其他内核(如ARM Cortex-A720或/和ARM Cortex-A520)在集群中配对。

Cortex-X4:https://en.wikipedia.org/wiki/ARM_Cortex-X4

Cortex-X4:Arm Introduces The Cortex-X4, Its Newest Flagship Performance Core

2. Cortex-A CPUARM Cortex-A是一组由Arm Holdings授权的32位和64位 RISC ARM处理器内核,这些内核旨在供应用程序使用。

Cortex-A:https://en.wikipedia.org/wiki/ARM_Cortex-A

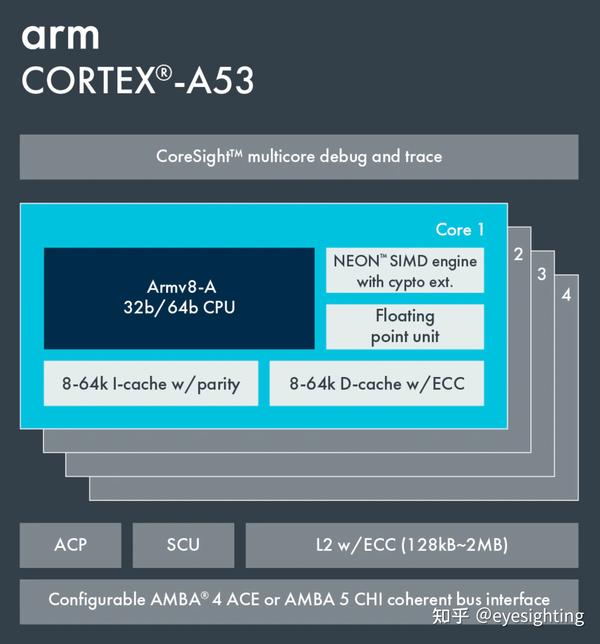

Cortex-A53

ARM Cortex-A53是首批实现ARMv8-A 64 位指令集的两个中央处理单元之一,该指令集由ARM Holdings剑桥设计中心设计,与Cortex-A57一起。Cortex-A53 是一款 2 宽解码 超标量处理器,能够双发出一些指令。它于 2012 年 10 月 30 日发布,并由 ARM 作为更强大的 Cortex-A57 微架构的独立、更节能的替代品进行营销,或者与big.LITTLE中更强大的微架构一起使用配置。与其他 ARM 知识产权和处理器设计一样, 它可作为IP 核提供给被许可人。

Cortex-A53:https://developer.arm.com/processors/cortex-a53

Cortex-A53:https://en.wikipedia.org/wiki/ARM_Cortex-A53

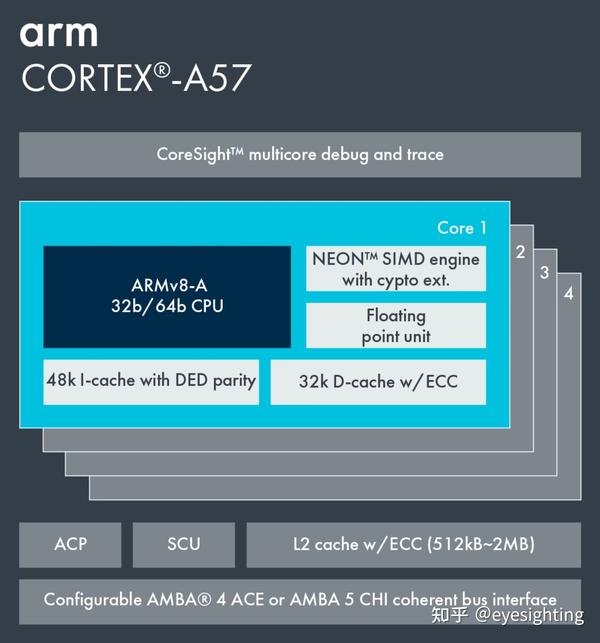

Cortex-A57

ARM Cortex-A57是实现ARM Holdings设计的ARMv8-A 64 位指令集的中央处理单元。Cortex-A57 是一个无序超标量管道。它可作为SIP 内核提供给被许可方,其设计使其适合与其他 SIP 内核(例如GPU、显示控制器、DSP、图像处理器等)集成到构成片上系统(SoC) 的一个芯片中。

Cortex-A57:Cortex-A57

Cortex-A57:https://en.wikipedia.org/wiki/ARM_Cortex-A57

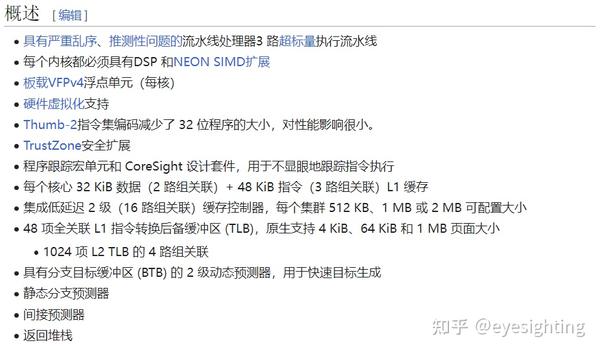

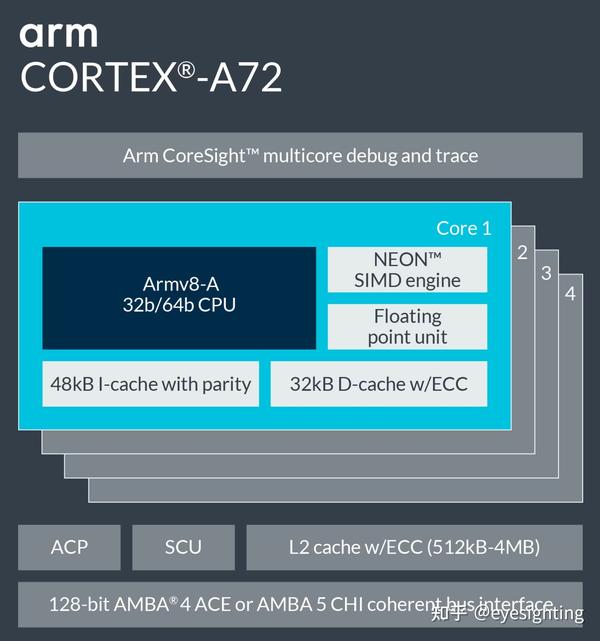

Cortex-A72

ARM Cortex-A72是一个执行ARMv8-A 64 位指令集的中央处理单元,由ARM Holdings的奥斯汀设计中心设计。Cortex-A72 是一个 3 路解码乱序超标量管道。[1] 它可作为SIP 内核提供给被许可方,其设计使其适合与其他 SIP 内核(例如GPU、显示控制器、DSP、图像处理器等)集成到构成片上系统的一个芯片中 (SoC)。Cortex-A72 于 2015 年宣布作为Cortex-A57的后继产品,旨在降低 20% 的功耗或提高 90% 的性能。

Cortex-A72:https://www.arm.com/products/silicon-ip-cpu/cortex-a/cortex-a72

Cortex-A72:Cortex-A72

Cortex-A72:https://en.wikipedia.org/wiki/ARM_Cortex-A72

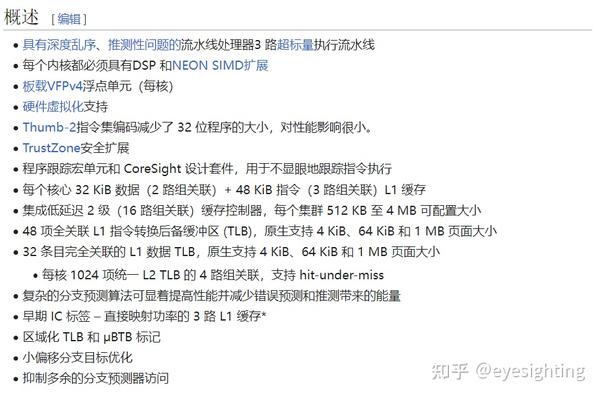

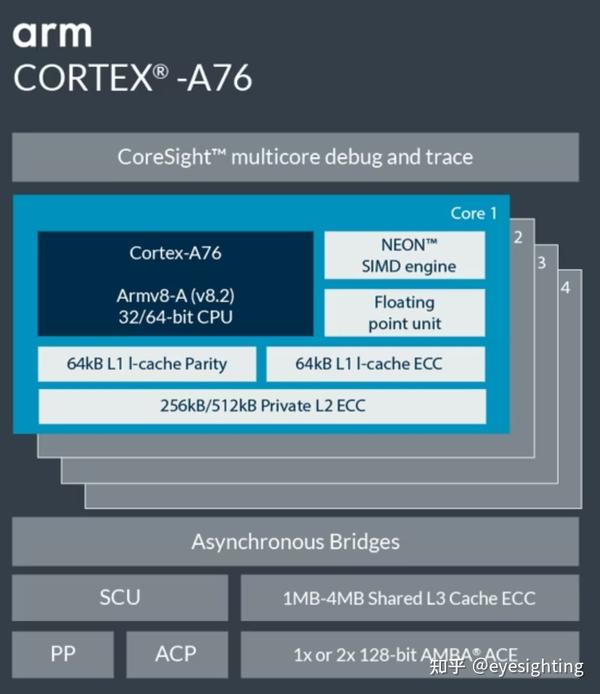

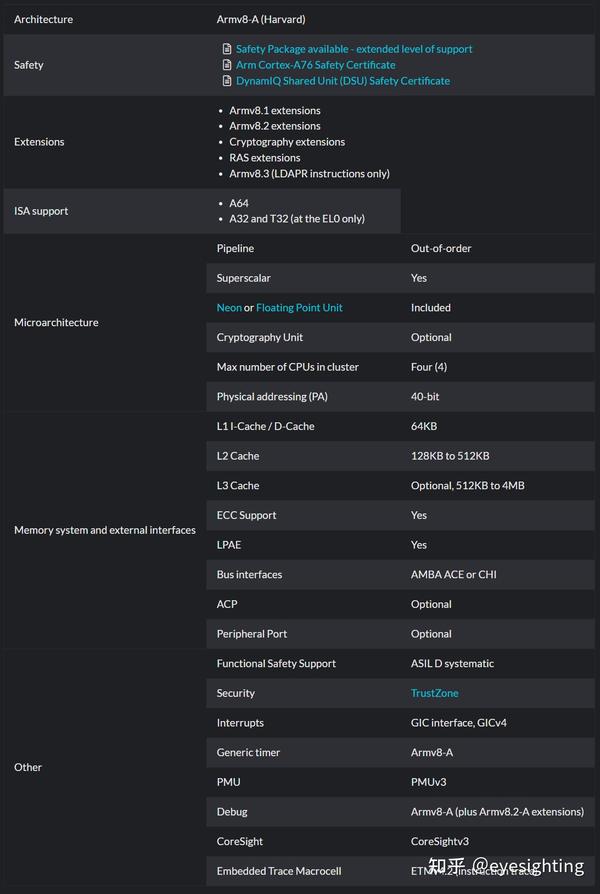

Cortex-A76

ARM Cortex-A76是执行ARMv8.2-A 64 位指令集的中央处理单元,由ARM Holdings奥斯汀设计中心设计。ARM 表示,与上一代Cortex-A75相比,整数和浮点性能分别提高了 25% 和 35% 。

Cortex-A76 前端采用 4 宽解码乱序 超标量设计。每个周期可以获取 4 条指令。重命名并调度 4 个 Mops,每个周期 8 个 µop 。无序窗口大小为 128 个条目。后端有 8 个执行端口,管道深度为 13 级,执行延迟为 11 级。

该内核支持非特权32位应用程序,但特权应用程序必须使用64位ARMv8-A ISA。[4]它还支持加载获取 (LDAPR) 指令 ( ARMv8.3-A )、点积指令 ( ARMv8.4-A )、PSTATE 推测存储绕过安全 (SSBS) 位和推测屏障 (CSDB、SSBB、PSSBB) 指令 ( ARMv8.5-A )。

内存带宽相对A75增加了90%。根据 ARM 的说法,A76 预计将提供 A73 两倍的性能,并且目标不仅仅是移动工作负载。该性能定位于“笔记本电脑级别”,包括Windows 10设备,与英特尔的Kaby Lake竞争。

Cortex-A76支持ARM的DynamIQ技术,与Cortex-A55高能效内核结合使用时,有望成为高性能内核。

Cortex-A76:Cortex-A76

Cortex-A76:https://en.wikipedia.org/wiki/ARM_Cortex-A76

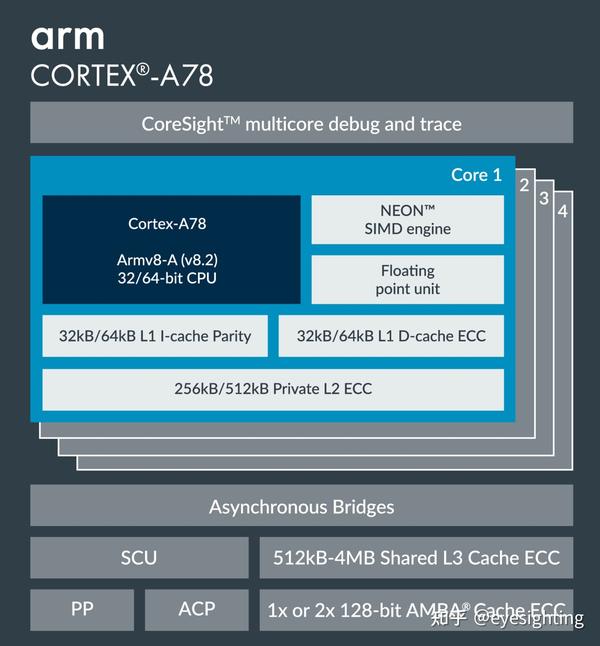

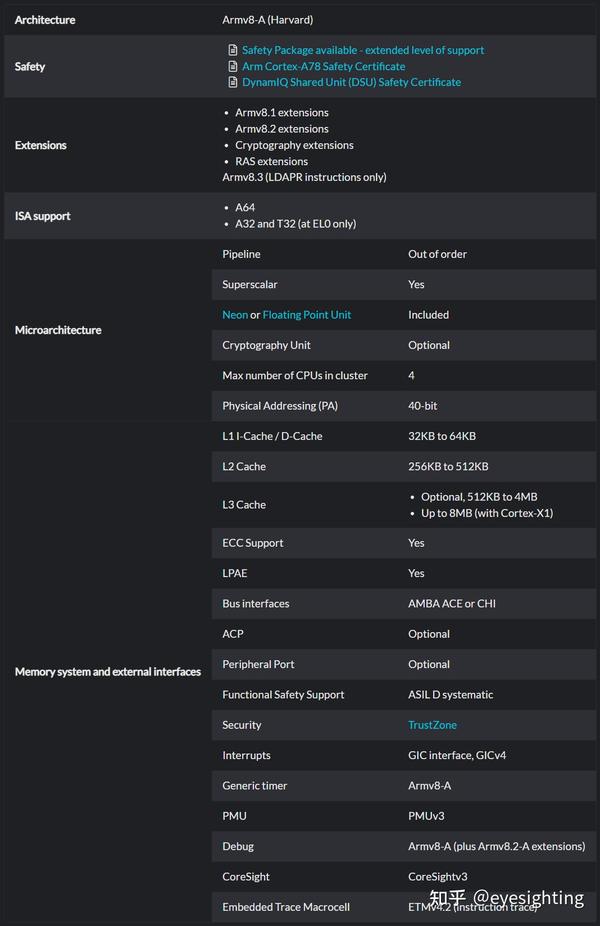

Cortex-A78

ARM Cortex-A78是一个中央处理单元,实现由ARM Ltd.奥斯汀中心设计的ARMv8.2-A 64 位指令集,用于高端设备。ARM Cortex-A78 是ARM Cortex-A77的后继产品。它可以与DynamIQ配置中的ARM Cortex-X1和/或ARM Cortex-A55 CPU配合使用,以提供性能和效率。该处理器还声称比其前代处理器节能高达 50%。

Cortex-A78 是一种 4 宽解码乱序 超标量设计,具有 1.5K 宏 OP (MOP) 缓存。它每个周期可以获取 4 条指令和 6 个 Mops,并且每个周期可以重命名和分派 6 个 Mops 和 12 µops。乱序窗口大小为160个条目,后端有13个执行端口,管道深度为13级,执行延迟由10级组成。

该处理器基于标准 Cortex-A 路线图构建,并提供 2.1 GHz ( 5 nm ) 芯片组,这使其在以下方面优于其前身: 性能提高 7% 功耗降低 4% 缩小 5%,意味着四核集群的服务面积增加 15%,额外的GPU、NPU。

Cortex-A78:https://www.arm.com/products/silicon-ip-cpu/cortex-a/cortex-a78

Cortex-A78:https://en.wikipedia.org/wiki/ARM_Cortex-A78

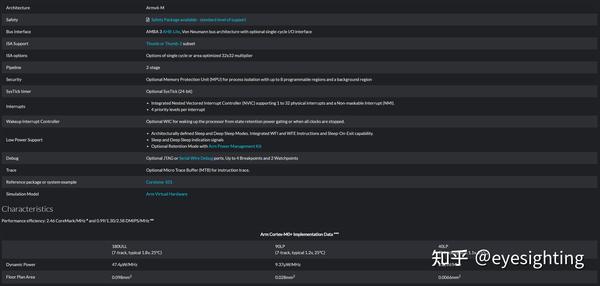

3. Cortex-M CPU

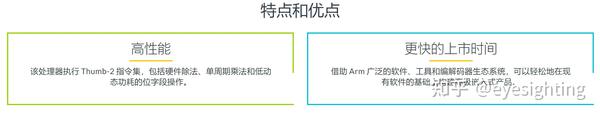

ARM Cortex-M是一组由ARM Limited授权的32 位 RISC ARM处理器内核。这些内核针对低成本、高能效的集成电路进行了优化,这些集成电路已嵌入到数百亿的消费设备中。[1] 虽然它们通常是微控制器芯片的主要组件,但有时它们也嵌入到其他类型的芯片中。

Cortex-M:https://en.wikipedia.org/wiki/ARM_Cortex-M

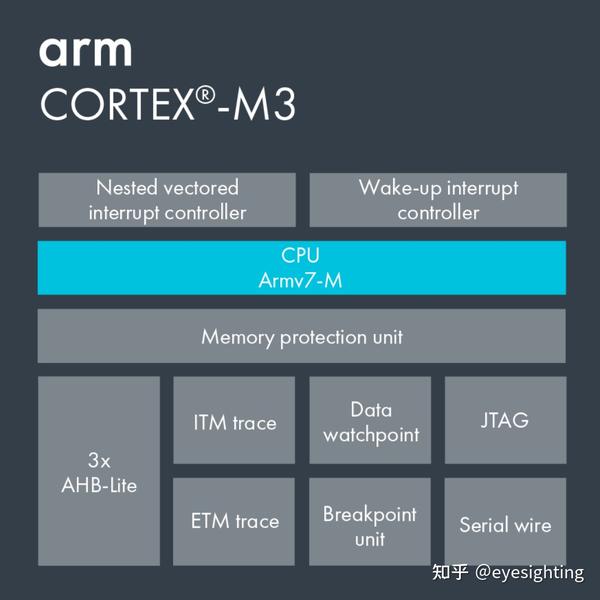

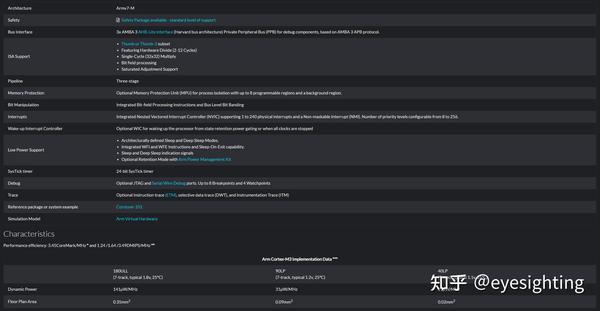

Cortex-M3

ortex-M3 处理器专为高性能、低成本平台而开发,适用于各种设备,包括微控制器、汽车车身系统、工业控制系统以及无线网络和传感器。

Cortex-M3:https://developer.arm.com/Processors/Cortex-M3

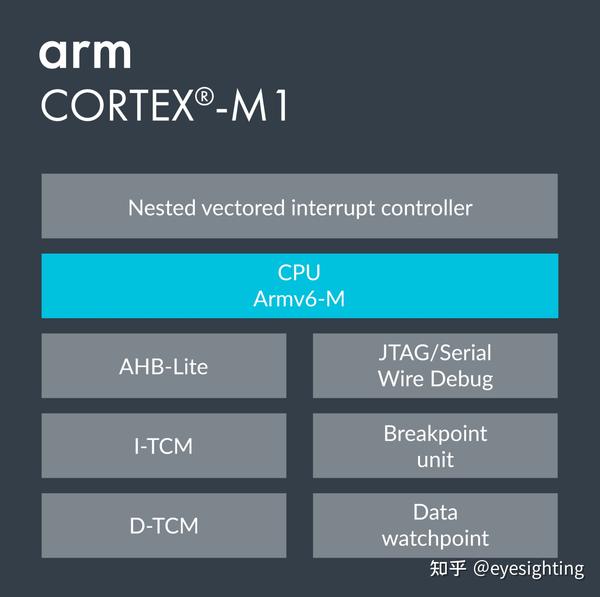

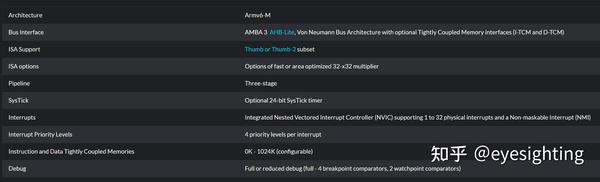

Cortex-M1

第一款专为在 FPGA 中实现而设计的 Arm 处理器。Cortex-M1 处理器面向 FPGA 设备,并支持领先的 FPGA 综合工具,使设计人员能够为每个项目选择最佳实施方案。Cortex-M1 处理器使 OEM 能够通过跨 FPGA、ASIC 和 ASSP 等多个项目的软件和工具投资合理化来实现显着的成本节省,并通过使用行业标准处理器实现更大的供应商独立性。

Cortex-M1:https://developer.arm.com/Processors/Cortex-M1Cortex-M0Arm

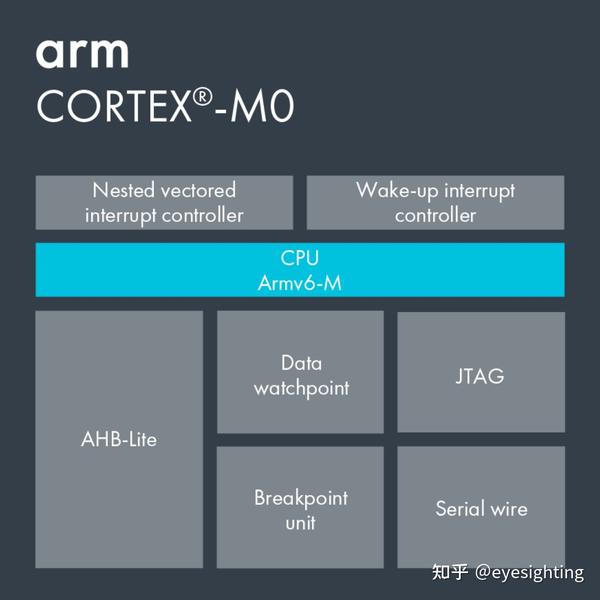

Cortex-M0

处理器是现有最小的 Arm 处理器之一。Cortex-M0 具有极小的硅面积、低功耗和最小的代码占用空间,使开发人员能够以 8 位价格点实现 32 位性能,从而绕过 16 位设备的步骤。该处理器的超低门数使其能够部署在模拟和混合信号设备中。

Cortex-M0:https://developer.arm.com/Processors/Cortex-M0

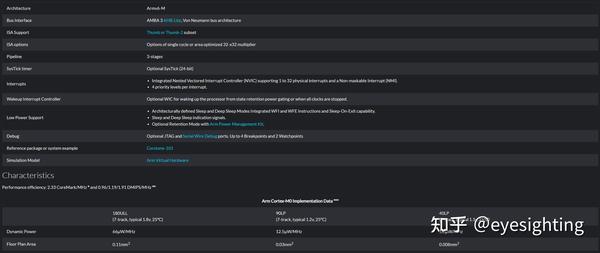

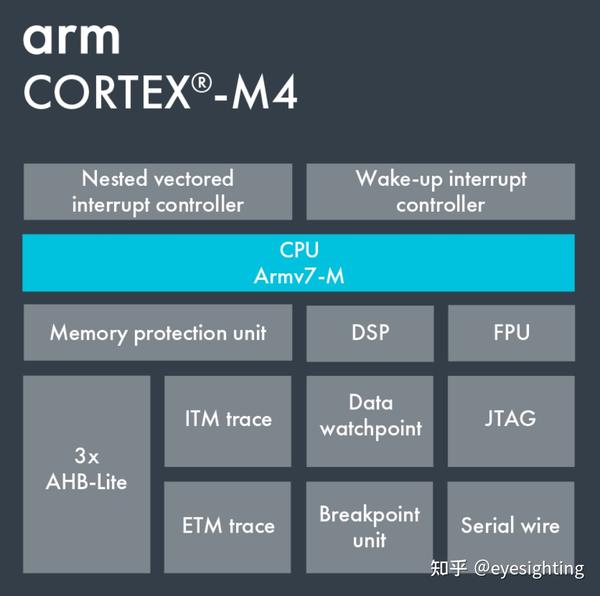

Cortex-M4

Arm Cortex-M4 处理器是一款高效嵌入式处理器。 Cortex-M4 处理器的开发是为了满足需要高效、易于使用的控制和信号处理功能组合的数字信号控制市场。Cortex-M 系列处理器将高效信号处理功能与低功耗、低成本和易于使用的优势相结合,满足了许多市场的需求。这些行业包括电机控制、汽车、电源管理、嵌入式音频和工业自动化市场。

Cortex-M4:https://developer.arm.com/Processors/Cortex-M4

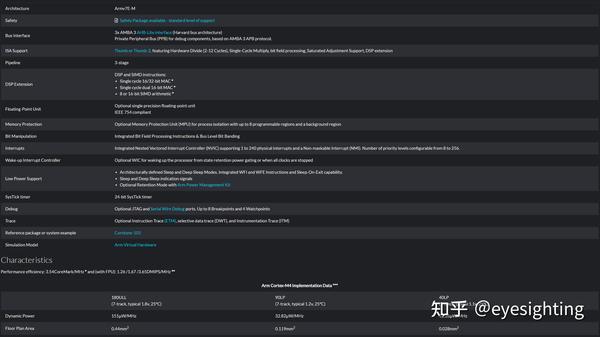

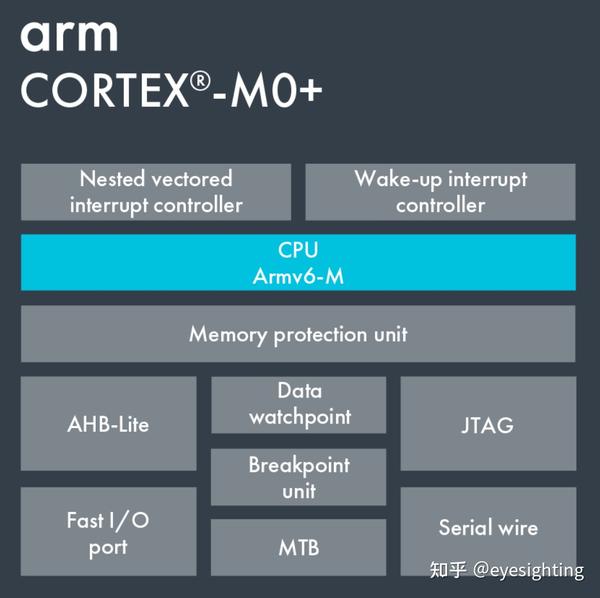

Cortex-M0+

Arm Cortex-M0+ 处理器是适用于受限嵌入式应用的最节能的 Arm 处理器。Cortex-M0+ 处理器建立在非常成功的 Cortex-M0 处理器的基础上,保留了完整的指令集和工具兼容性,同时进一步降低了能耗并提高了性能。Cortex-M0+ 极小的硅面积、低功耗和最小的代码占用空间使开发人员能够以 8 位价格点实现 32 位性能,从而绕过 16 位设备的步骤。Cortex-M0+ 处理器提供多种选项以提供灵活的开发。

Cortex-M0+:https://developer.arm.com/Processors/Cortex-M0-Plus

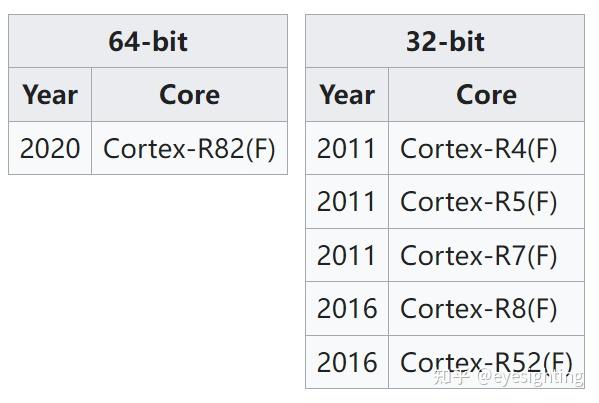

4. Cortex-R CPU

ARM Cortex-R是由Arm Holdings授权的32 位和64 位 RISC ARM处理器内核系列。这些内核针对硬实时和安全关键型应用进行了优化。该系列中的内核实现 ARM 实时 (R) 配置文件,这是三种架构配置文件之一,另外两个是 Cortex-A 系列实现的应用程序 (A) 配置文件和 Cortex-M 实现的微控制器 (M )配置文件家庭。

Cortex-R:https://en.wikipedia.org/wiki/ARM_Cortex-R

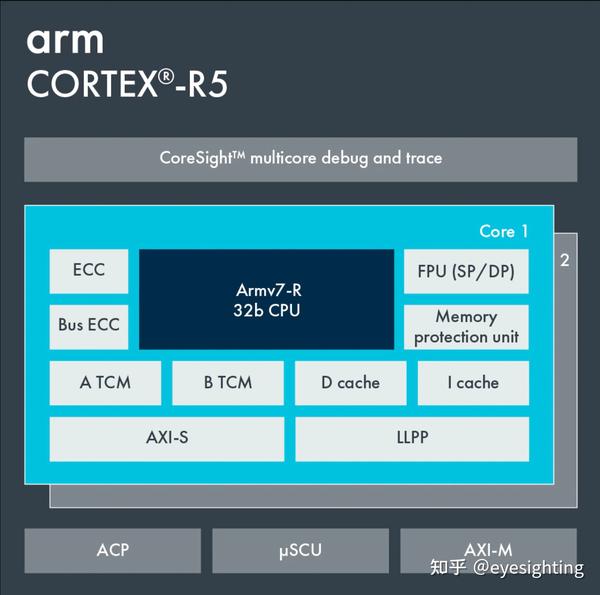

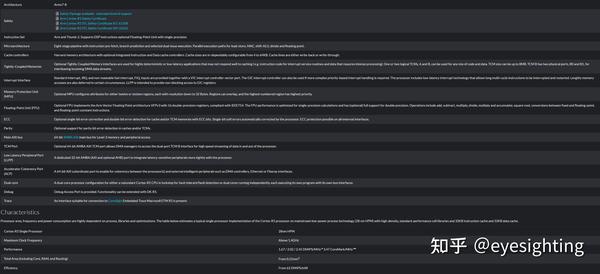

Cortex-R5

Arm Cortex-R5 处理器为实时应用提供扩展的故障遏制。Cortex-R5 处理器基于 Cortex-R4 的功能集构建,具有增强的错误管理、扩展的功能安全和 SoC 集成功能,适用于深度嵌入式实时和安全关键系统。

Cortex-R5:https://developer.arm.com/Processors/Cortex-R5

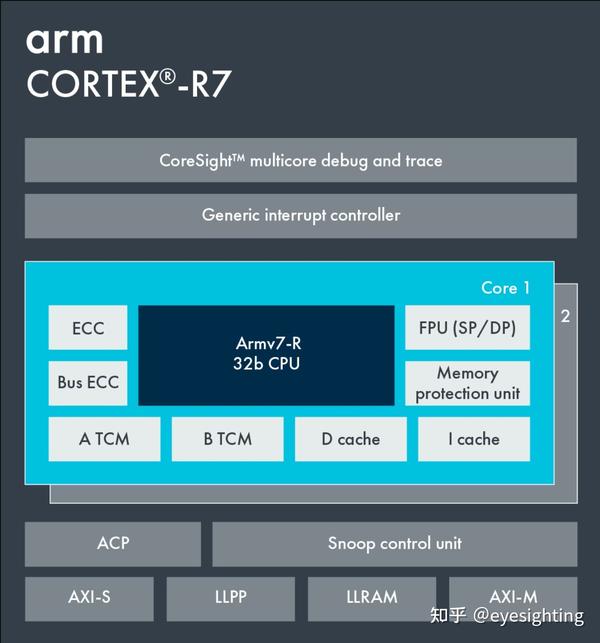

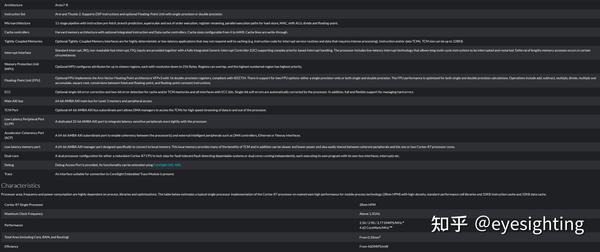

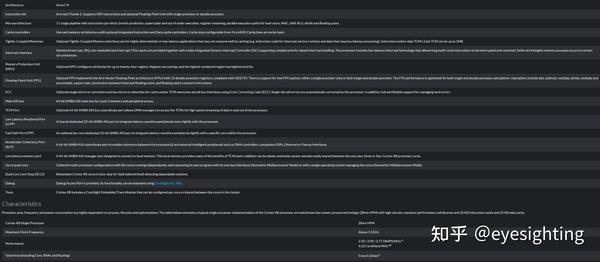

Cortex-R7

Cortex-R7 处理器具有 11 级超标量无序流水线,具有动态和静态分支预测、动态寄存器重命名和非阻塞加载存储单元。还有一个集成的通用中断控制器 (GIC)、监听控制单元 (SCU) 和定时器,可进一步减少延迟并在双核配置中实现对称多处理。

Cortex-R7:https://developer.arm.com/Processors/Cortex-R7

Cortex-R8

Cortex-R8 处理器在同类实时处理器中具有最高的性能。它是一个基于Armv7-R架构的32位内核,具有11级流水线和超标量乱序执行。Cortex-R8 可以从单核配置扩展到四核配置,以利用工作负载并行性。可以根据工作负载关闭各个内核的电源。

Cortex-R8:https://developer.arm.com/Processors/Cortex-R8

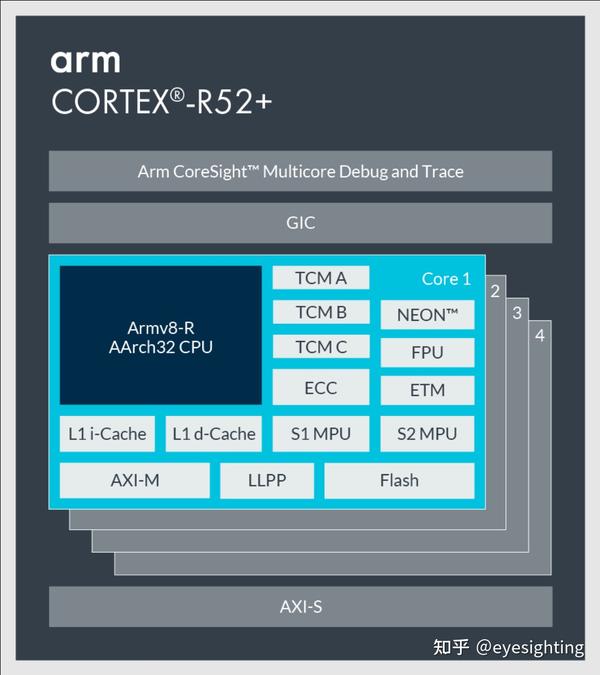

Cortex-R52+

Arm Cortex-R52+ 处理器的软件与 Cortex-R52 兼容,为实时功能安全应用提供改进的虚拟化和简化的系统集成。Cortex-R52+ 处理器为具有功能安全要求的实时应用提供了改进的可配置性。它实现了 Armv8-R 架构,并提供增强的虚拟化粒度,使系统能够扩展虚拟机的分离。

Cortex-R52+:https://developer.arm.com/Processors/Cortex-R52%20Plus

5. Immortalis GPU

全新Immortalis旗舰图形处理单元 (GPU) ,最佳体验永存、释放游戏性能,首款支持光线追踪的 ARM GPU。

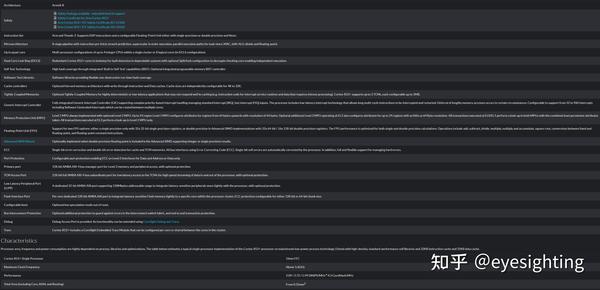

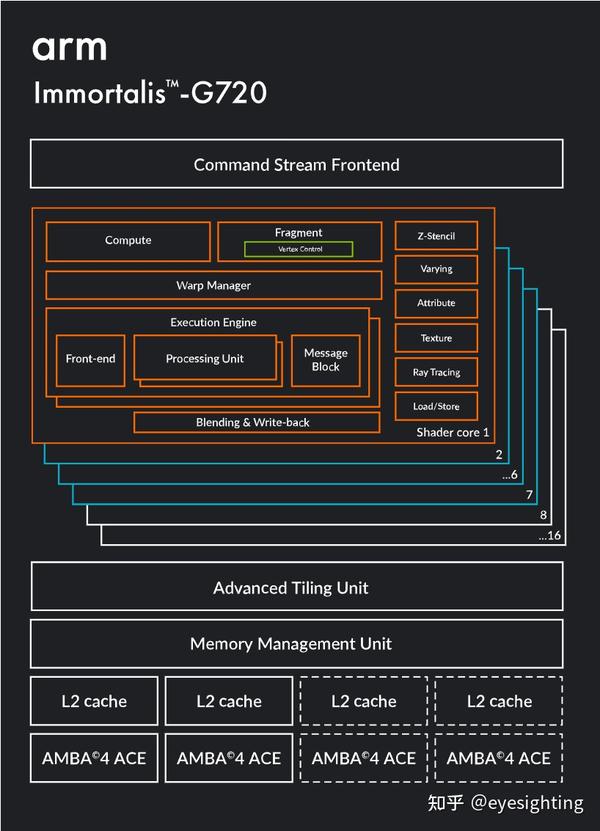

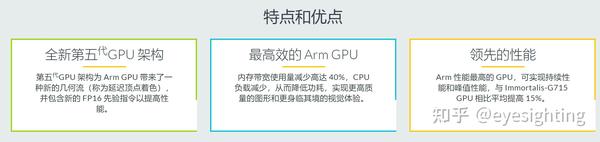

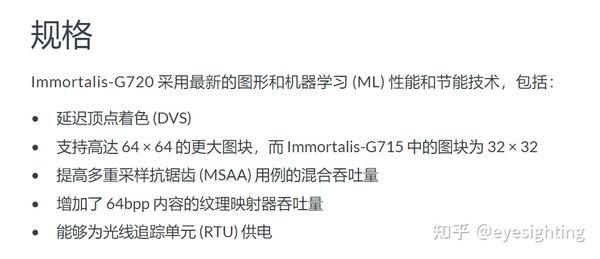

Immortalis-G720

通过 Arm 上的 Immortalis 体验移动未来:首款基于 Arm 第五代架构、专为旗舰智能手机设计的 GPU。Immortalis-G720 提供改进的性能并减少内存带宽使用,从而实现更好、更持久的帧速率,最终实现比以往更高质量的图形,带来更身临其境的视觉体验。这是我们有史以来性能最高、效率最高的 GPU。

Immortalis-G720:Immortalis-G720

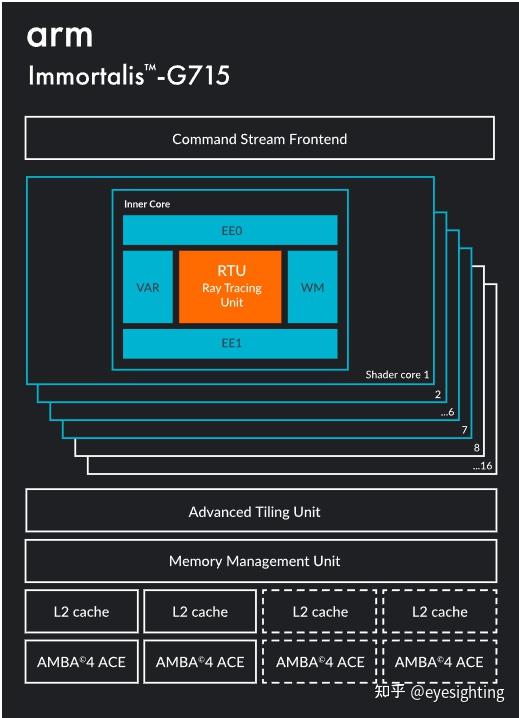

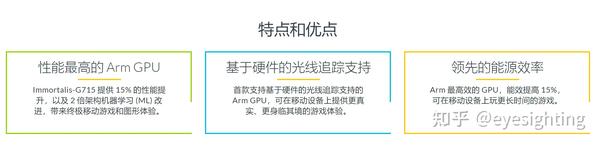

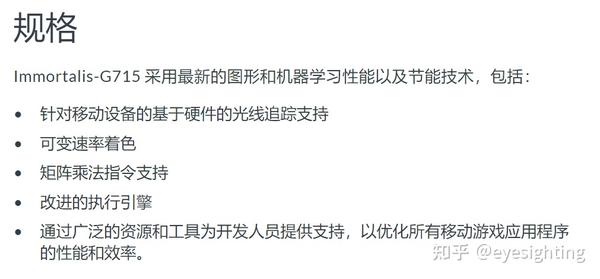

Immortalis-G715

释放游戏性能:Immortalis-G715 是 Arm 全新旗舰 GPU,旨在为下一代旗舰智能手机提供极致游戏体验。它是首款在移动设备上提供基于硬件的光线追踪支持的 Arm GPU,将 Android 上的移动游戏推向了一个全新的水平。

Immortalis-G715:Immortalis-G715

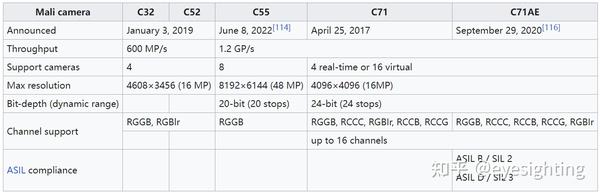

6. Mali-C ISP

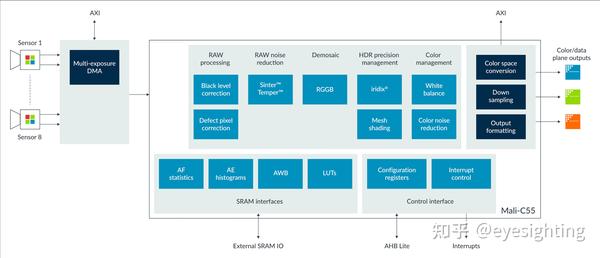

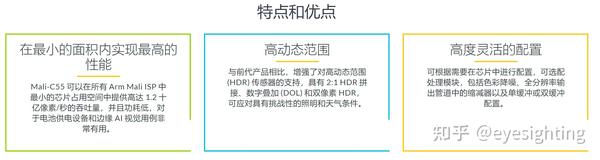

Mail-C55

适用于计算机视觉和智能显示系统的多功能图像信号处理器:Arm Mali-C55 图像信号处理器 (ISP) 为各种物联网、嵌入式和机器学习 (ML) 应用提供高分辨率图像处理、能源效率和无与伦比的图像质量的最佳组合,包括智能相机(例如用于消费者和商业安全的智能相机)、业余爱好无人机和机器人、机顶盒和 AR 可穿戴设备。

Mail-C55:https://www.arm.com/products/silicon-ip-multimedia/image-signal-processor/mali-c55

Mail-C55:https://developer.arm.com/Processors/Mali-C55

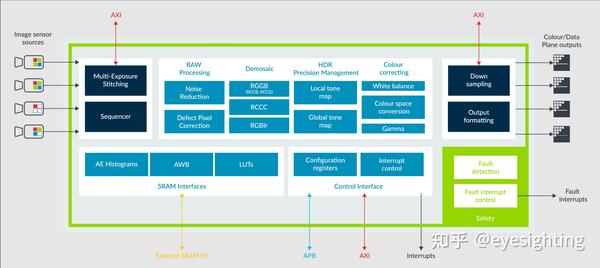

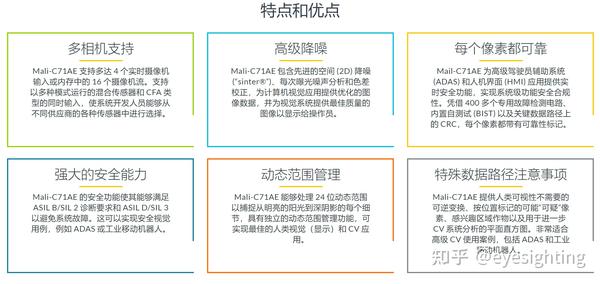

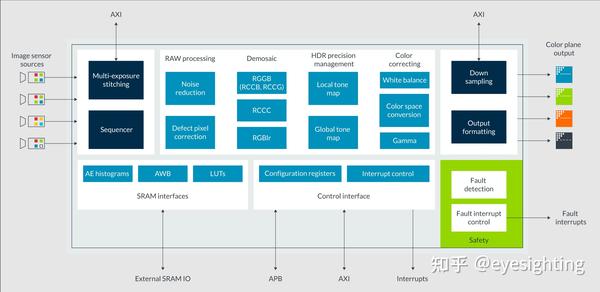

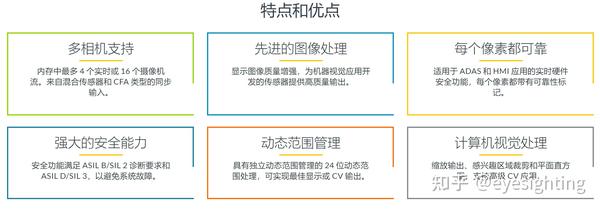

Mail-C71AE

Mali-C71AE 是 Arm 专为新兴智能汽车系统和工业市场开发的最高性能图像信号处理器 (ISP)。Mali-C71AE 向计算机视觉 (CV) 系统和人类显示器提供关键视觉信息,以实现清晰、方便的查看,是 Mali Camera 系列 ISP 中首款具有功能安全应用内置功能的产品。

Mail-C71AE:https://www.arm.com/products/silicon-ip-multimedia/image-signal-processor/mali-c71ae

Mail-C78AE:Mali-C71AE

Mail-C78AE

Arm Mali-C78AE 以 Mali-C71AE ISP 的高性能为基础,并结合了适用于 IoT 的 Mali-C52 中领先的图像质量性能。它专为汽车 ADAS 和显示应用而设计,这些应用共享这两种功能的摄像头。

Mail-C78AE:https://www.arm.com/products/silicon-ip-multimedia/image-signal-processor/mali-c78ae

Mail-C78AE:https://developer.arm.com/Processors/Mali-C78AE

7. Mail-G GPU

Mali系列图形处理单元(GPU)和多媒体处理器是Arm Holdings生产的半导体知识产权核心,并授权Arm合作伙伴 进行各种ASIC设计。 Mali GPU 由Falanx Microsystems A/S开发,该公司是挪威科技大学一个研究项目的衍生产品。Arm Holdings于 2006 年 6 月 23 日收购了 Falanx Microsystems A/S,并将该公司更名为Arm 挪威。该团队最初名为Malaik,后来将其缩写为Mali(塞尔维亚-克罗地亚语) , 意为“小”,这被认为适合移动 GPU。

Mail GPU:https://en.wikipedia.org/wiki/Mali_(processor)

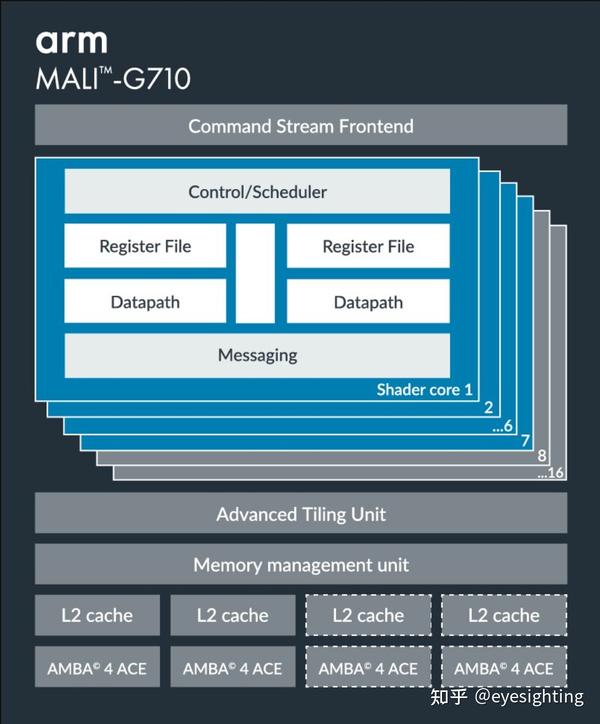

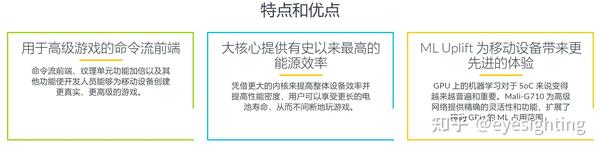

Mail-G710

适用于高端市场的第三代基于 Valhall 的图形处理单元 (GPU):Mali-G710 以 Mali GPU 的高性能路线图为基础,通过改变游戏规则的功能实现高性能游戏。命令流前端的引入和重新设计的执行引擎最大限度地提高了下一代设备的性能效率。

Mail-G710:Mali-G710

Mial-G710:Mali-G710

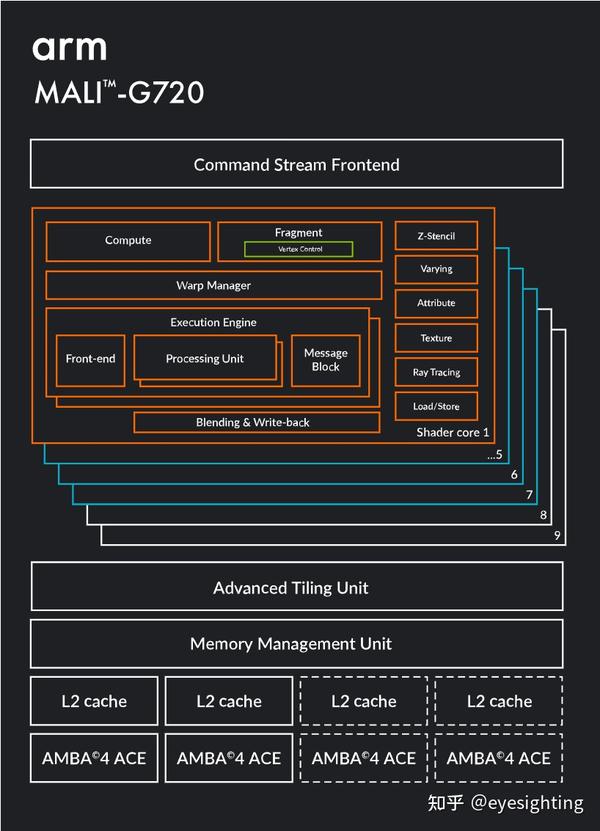

Mail-G720

Mail的下一代视觉计算:Mali-G720 采用 Arm 第五代架构设计,可提高性能,同时降低内存带宽使用、功耗和 CPU 负载。Mali-G715 GPU 比其前身更强大,充分利用先进的 GPU 技术,可以为各种设备上的沉浸式游戏和智能 AI 应用程序提供支持。

Mail-G720:Mali-G720

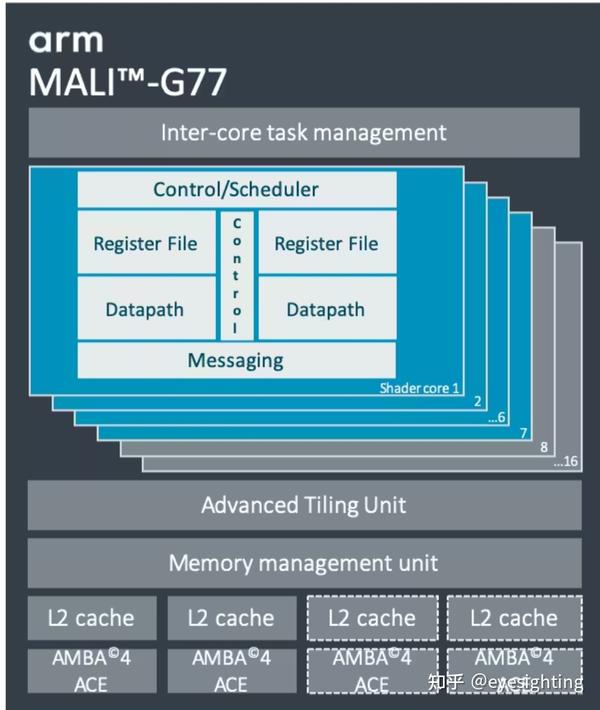

Mail-G77

不折不扣的图形性能:适用于高端市场的第一代基于 Valhall 的图形处理单元 (GPU)。Mali-G77 提高了能源效率并提升了性能密度,成为适用于图形和设备上机器学习等复杂用例的性能最高的移动 GPU,并为高保真游戏工作负载提供一致的电池寿命改进。

Mail-G77:Mali-G77

8. Mail-V VPU

Mila-V500

Mila-V550

9. Ethos NPU

Ethos是Arm为物联网和边缘应用设计的一系列可合成 神经处理器IP 。

Ethos NPU:Ethos – ARM – WikiChip

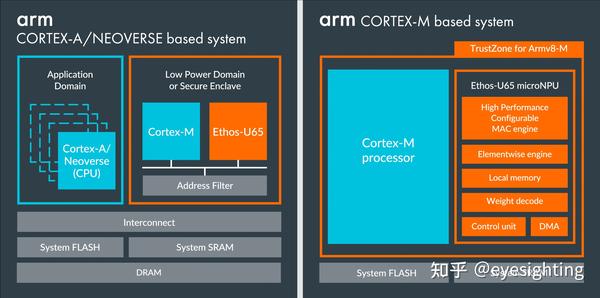

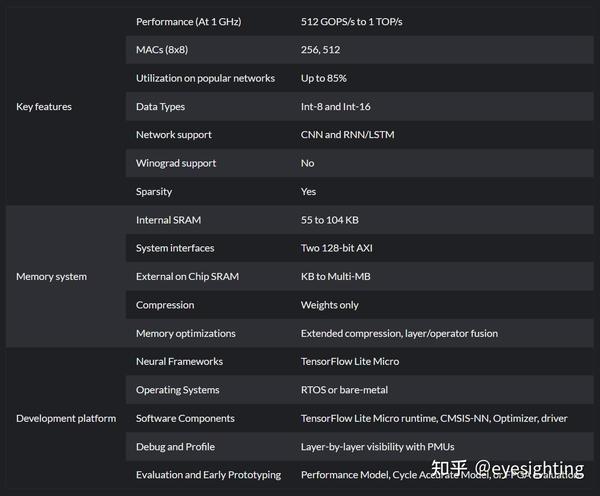

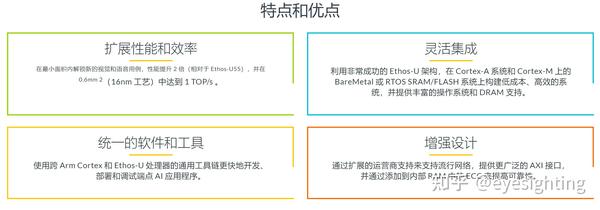

Ethos-U65

边缘和端点设备的人工智能创新:利用 Arm Ethos-U microNPU 系列的最新成员,在各种嵌入式设备中构建低成本、高效的 AI 解决方案。Ethos-U65 保持了 Arm Ethos-U55 的功效,同时将其适用性扩展到基于 Arm Cortex-A、Cortex-R 和 Neoverse 的系统,同时提供两倍的设备上机器学习 (ML) 性能。

Ethos-U65:Ethos-U65

Ethos-U65:https://www.arm.com/products/silicon-ip-cpu/ethos/ethos-u65

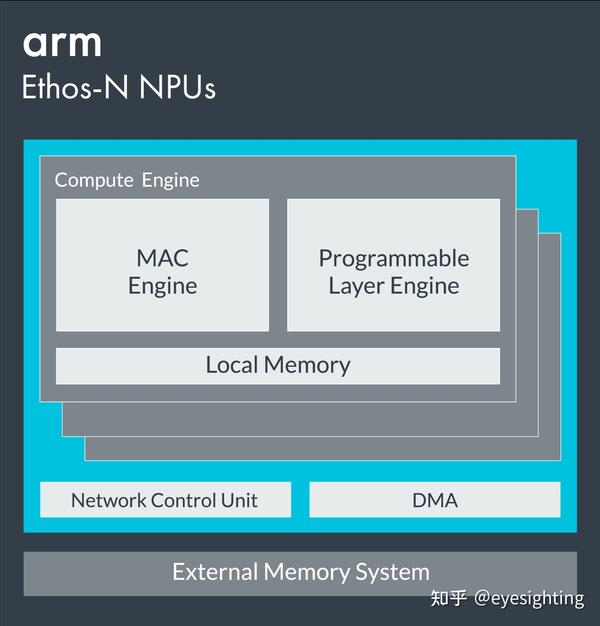

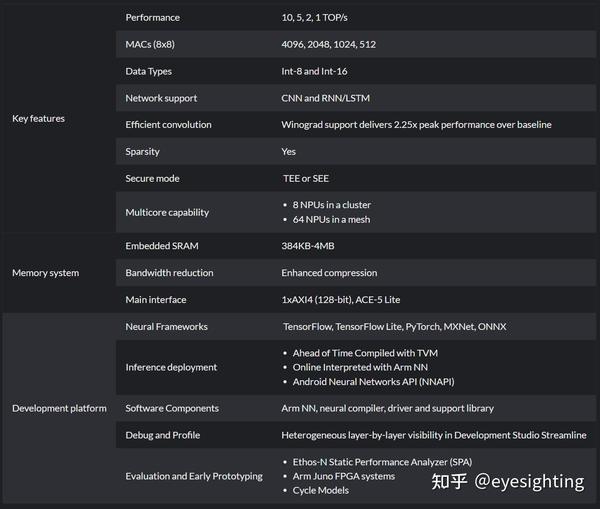

Ethos-N78

高度可扩展且高效的第二代机器学习推理处理器,在多个细分市场以低成本构建优质人工智能解决方案:Ethos-N78 是 Arm 的第二代高度可扩展且高效的 NPU,可实现新的沉浸式应用,单核性能提高 2.5 倍,现在可通过多核技术从 1 TOP/s 扩展到 10 TOP/s 甚至更高。它通过 90 多种配置提供了优化 ML 功能的灵活性。

Ethos-N78:Ethos-N78

Ethos-N78:Ethos-N78

10. Eoverse-N DPU

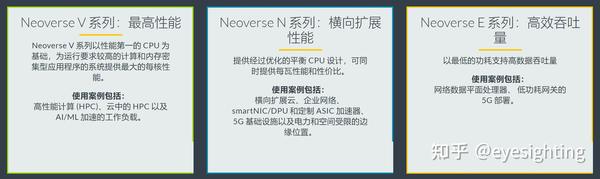

借助 Arm Neoverse 从云端到边缘的一流性能。全球基础设施正在迅速变化,以适应不断增长的工作负载和不断提高的性能需求。Arm Neoverse 针对云、边缘和 5G 网络进行了优化,可提供未来基础设施及其客户所需的速度、能效、每瓦性能和性价比。Arm Neoverse 系列旨在面向广泛的基础设施市场。

Arm Eoverse :https://www.arm.com/products/silicon-ip-cpu/neoverse

https://en.wikipedia.org/wiki/ARM_Neoverse

Neoverse-N1

Neoverse-N1:Neoverse N1

Neoverse-N2

Neoverse-N2:Neoverse N2

10. Eoverse-E DPU

Neoverse-E1

Neoverse-E1:Neoverse E1

10. Eoverse-V DPU

Neoverse-V1

Neoverse-V1:Neoverse V1

11. SDK

11.1 ArmNN SDK

Arm NN SDK 是一套免费的开源 Linux 软件工具,可在节能设备上实现机器学习工作负载。该推理引擎在现有神经网络框架和高能效 Arm Cortex-A CPU、Arm Mali GPU 和 Ethos NPU 之间架起了一座桥梁。

ArmNN SDK:https://www.arm.com/products/silicon-ip-cpu/ethos/arm-nn

ArmNN SDK:https://github.com/ARM-software/armnn

11.2 Compute Library

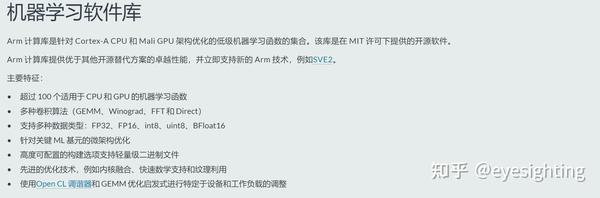

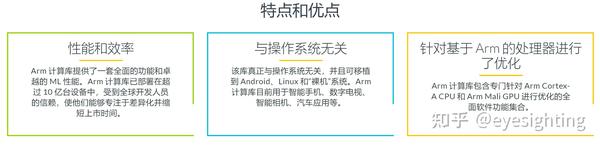

机器学习软件库:Arm 计算库是针对 Cortex-A CPU 和 Mali GPU 架构优化的低级机器学习函数的集合。

Compute Library:Compute Library – Arm®

Compute Library:Compute Library – Arm®

Compute Library:https://github.com/ARM-software/ComputeLibrary

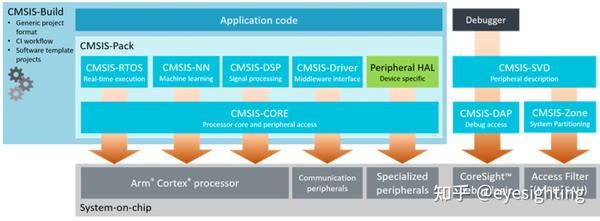

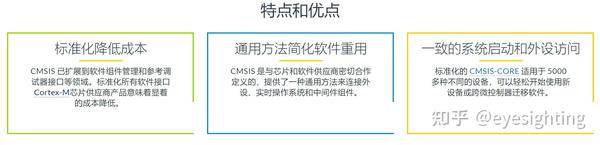

11.3 CMSIS通用微控制器软件接口标准 (CMSIS):CMSIS 能够为处理器及其外设提供一致的设备支持和简单的软件接口,从而简化软件重用、缩短微控制器开发人员的学习曲线,并缩短新设备的上市时间。

CMSIS:CMSIS

CMSIS:Introduction

CMSIS:GitHub – ARM-software/CMSIS_5: CMSIS Version 5 Development Repository

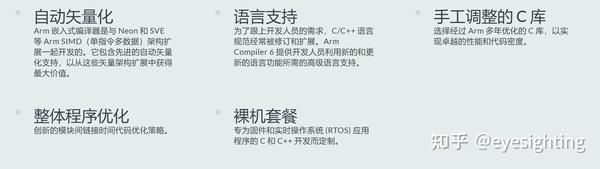

11.4 C/C++Compilers

几十年来,Arm 的 CPP 编译器受到数十万 C/C++ 开发人员的信赖,已用于构建数十亿设备中提供的代码。它支持开发高效产品,充分利用 Arm Cortex 处理器和架构(从 Armv6-M 到 Armv8-A 64 位 Arm)的所有功能。

C/C++Compilers:CPP Compiler Enables Highly-Efficient Product Development

12. Stack

Arm Developer:Documentation – Arm Developer

12.1 Floating Point

对浮点运算的高性能硬件支持:Arm架构为半精度、单精度和双精度算术中的浮点运算提供高性能和高效率的硬件支持。浮点数据类型对于各种数字信号处理 (DSP) 应用至关重要。许多应用程序本质上受益于浮点的动态范围和精度,以处理大型数据集或范围不可预测的数据集。

Arm Floating Point:Floating-point – Arm®

12.2 DSP

具有数字信号处理功能的 Trusted Arm 处理器:随着家庭变得更加智能,设备界面变得更加人性化,设备必须能够连接模拟世界和数字世界。这推动了比以往更多的设备上处理,以及跨许多应用程序(从语音到音频到传感器集线器再到机器学习(ML))的先进传感、计算和可扩展性。无论多传感器设备是否需要专用数字信号处理 (DSP) 硬件,Arm 及其合作伙伴都能提供设备上处理能力的显着提升。这使得公司能够广泛创新并扩展其产品,同时满足广泛的要求和应用。Arm CPU 中的 DSP 扩展使得无论专业知识如何,都可以使用 DSP 功能。借助单个处理器中的高效控制代码和高性能 DSP,设计人员可以在不影响性能的情况下降低成本、面积和复杂性。

Arm DSP:What is DSP? – Digital Signal Processing Chip – Arm®

Arm DSP:What is DSP? – Digital Signal Processing Chip – Arm®

12.3 NEON

Arm Neon 是适用于 Arm Cortex-A 和 Arm Cortex-R 系列处理器的高级单指令多数据 (SIMD) 架构扩展,其功能可极大改善移动设备上的使用案例,例如多媒体编码/解码、用户界面、2D/3D 图形和游戏。Neon 还可以加速信号处理算法和功能,以加快音频和视频处理、语音和面部识别、计算机视觉和深度学习等应用的速度。Neon 指令最多允许:16×8 位、8×16 位、4×32 位、2×64 位整数运算;8×16位、4×32位、2×64位浮点运算。

Arm NEON:https://developer.arm.com/Architectures/Neon

Arm NEON:https://www.arm.com/technologies/neon

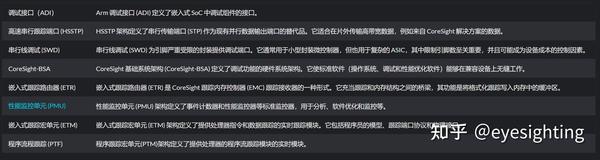

12.4 CoreSight

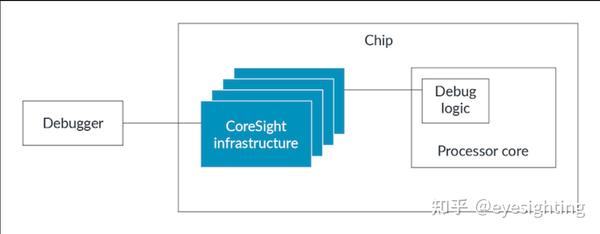

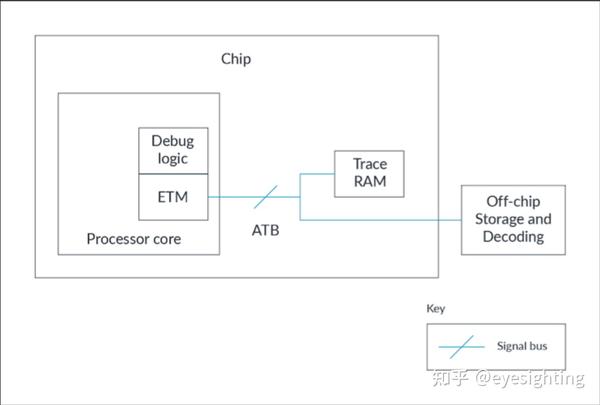

CoreSight 架构提供了一组标准接口和程序员模型视图,使合作伙伴能够定义 CoreSight 组件并将其集成到 CoreSight 基础架构中。

CoreSight:CoreSight Architecture

CoreSight:Documentation – Arm Developer

12.5 TtrustZone

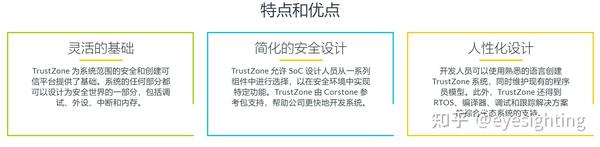

什么是 TrustZone 技术:基于 Cortex-A 的应用处理器内的 TrustZone 技术通常用于运行可信启动和可信操作系统,以创建可信执行环境 (TEE)。典型用例包括保护身份验证机制、加密、移动设备管理、支付、密钥材料和数字版权管理 (DRM)。

Cortex-A 的 TrustZone 如何工作:TrustZone 方法的核心是安全和非安全世界的概念,这些世界是硬件分离的,非安全软件被阻止直接访问安全资源。在 Arm Cortex-A 处理器中,软件要么驻留在安全世界,要么驻留在非安全世界;两者之间的切换是通过称为安全监视器的软件来完成的。这种安全(可信)和非安全(不可信)世界的概念超出了处理器范围,涵盖了 SoC 内的内存、软件、总线事务、中断和外设。

适用于 Arm Cortex-M 处理器的 TrustZone 技术可以在所有成本点为物联网设备提供强大的保护级别。该技术通过将关键安全固件、资产和私人信息与应用程序的其余部分隔离来降低遭受攻击的可能性。它为根据平台安全架构 (PSA) 准则建立设备信任根提供了完美的起点。

适用于 Arm Cortex-M 处理器的 TrustZone 技术可以在所有成本点为物联网设备提供强大的保护级别。该技术通过将关键安全固件、资产和私人信息与应用程序的其余部分隔离来降低遭受攻击的可能性。它为根据平台安全架构 (PSA) 准则建立设备信任根提供了完美的起点。

TtrustZone Cortex-A:TrustZone for Cortex-A – Arm®

TtrustZone Cortex-M:TrustZone for Cortex-M – Arm®

12.6 SecurCore

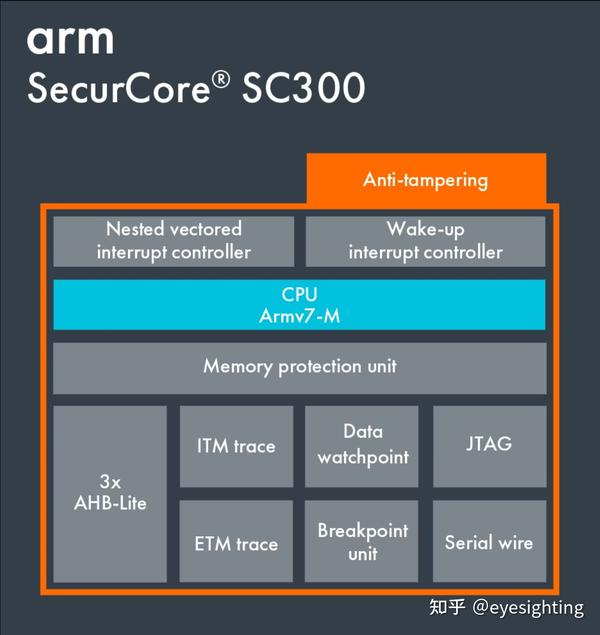

专为高性能嵌入式安全应用而设计:Arm SecurCore 处理器具有防篡改功能。SC300 嵌入了针对侧通道攻击和故障注入的对策。

Arm SecurCore SC300:SecurCore SC300

Arm SecurCore SC300:SC300

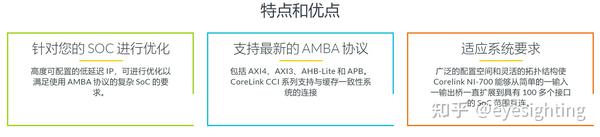

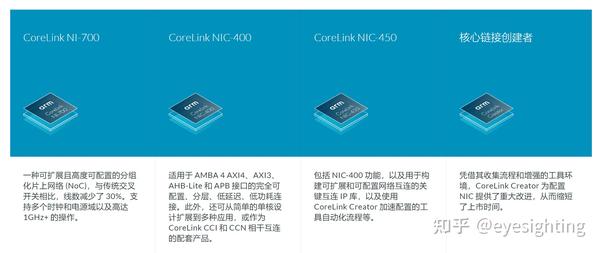

12.7 CoreLink

用于 SoC 连接的高度可配置拓扑:Arm CoreLink 网络互连可在多种应用中进行配置,从单个桥接组件到复杂的基础设施。

CoreLink NIC:CoreLink NIC for SoC Connectivity – Arm®

CoreLink NIC:CoreLink NIC for SoC Connectivity – Arm®

CoreLink CI700:CoreLink CI-700

总结自动驾驶SOC、MCU平台的芯片几乎都离不开Arm的IP、架构、软硬件产品。

发表回复